What is pipelining in computer architecture?

What is Pipelining?

A simple question that students ask is “what is pipelining in computer architecture? A method that accumulates commands from the processor and overlapped during the execution using pipelines is known as pipelining.

- The system hardware is planned in such a way so that there is an increase in performance

- The main aim of pipelining is that it supplies and executes the instructions in order that is one by one and it is termed pipeline processing.

- It can organize multiple commands at the same time. In pipelining processing, each instruction is mainly divided into smaller fragments and then each part does the specified task allotted to it.

Implementation:

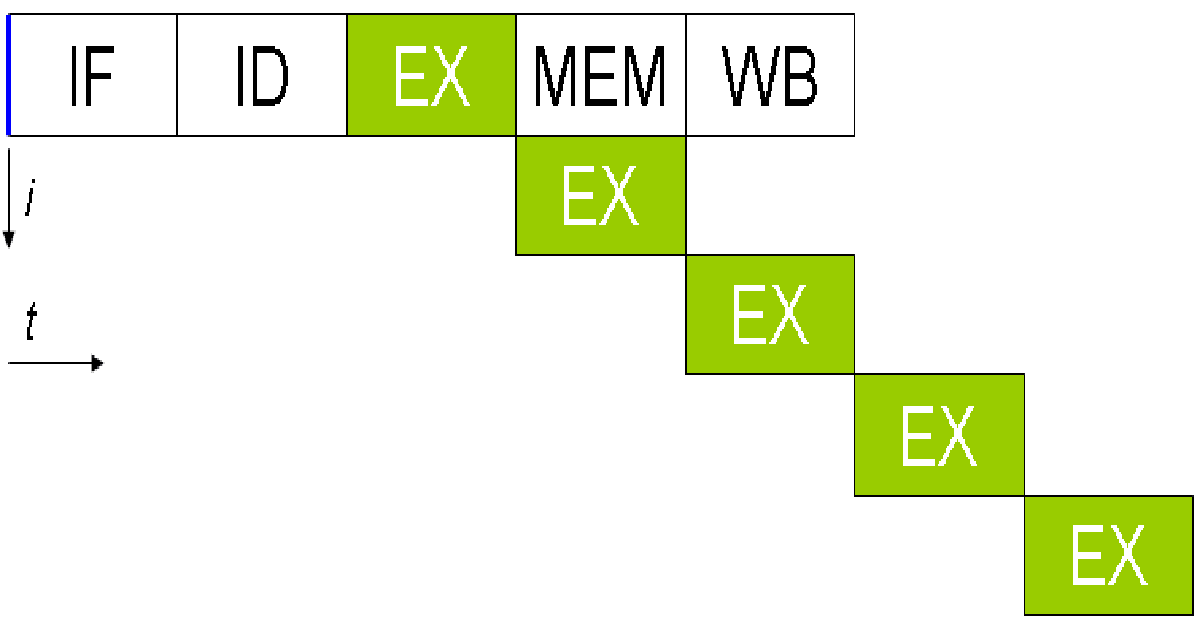

There are mainly 5 stages to implement the pipelining

- Instruction fetch

- Instruction decodes

- The Instruction executes

- Memory access

- Writeback

Instruction fetch:

In this phase, the processor reads the commands from the memory using a particular address and the value of the command or the address mainly kept in the program counter. It loads the information from the memory storage to the register of the CPU. The time it takes fetch command is identified as fetch time and it is calculated in clock ticks.

Instruction decode:

The address we get is then decoded to get the deposited values at that register address. It determines what command is to be completed so that it could be recognized that how many and which operands are needed to implement the instruction. While interpreting the opcode is also interpreted to get the subsequent steps to be performed on the instruction and they are moved to explicit registers.

Instruction execute:

Instructions are executed in a manner that is primarily read by the instruction pipeline and in the meantime, the instruction that arrived before this instruction is being performed in some other part of the pipeline. By this, we can implement numerous instructions at a time and the effectiveness of the pipeline can be increased if we allocate equivalent duration to the instruction cycle. All the arithmetic is performed throughout this stage.

Memory access:

In this phase, the operands of memory are read from or to memory that is existing in the instruction. It offers the memory access that is required for the instruction under execution. In case if it loads at that time it will load operand from the memory and likewise, if it stores at that time it will store operand into memory.

Write back:

At this phase, all the actions that are made on the instruction are written back to the registered address given at the start. It is the end stage so no more action will be made other than to write all the data back to the register by means of the address.

Hazards of pipelining:

These are some circumstances that stop the subsequent instruction in the instruction stream from implementing in its chosen time cycle. (What is pipelining in computer architecture?)

If a pipeline must wait due to some purpose it is known as a pipeline hazard.

There are mainly three classes of hazards

- Data hazard

- Structural hazard

- Control hazard

Data hazard:

This hazard occurs due to the modification in the data in diverse stages of the pipeline. For instance, data in the two phases are changed that is needed for the subsequent stage and it will cause since It will no more be effectual, and it is termed as race hazard.

There are mainly 3 situations in which this hazard can arise:

- RAW (Read after Write) and it a true dependency

- WAR (Write after Reading) is anti-dependency

- WAW (Write after write) is output dependency

Structural hazard:

The structural hazard occurs for the reason of the conflict in the resources that means the assessable resources are not supporting the combinations of commands. The conflict in resources demarcated that there are generally two instructions in the pipeline, and they require the same resource. It refers that only one command can use the resources and they will work in sequence and not in a similar fashion for a certain portion of the pipeline. This is also known as a resource hazard.

If we take a specimen if there are many commands that are ready to go o the implementation stage and it has a single arithmetic and logic unit. To resolve this sort of hazard we must raise the number of resources, for instance, multiple ports and many ALU so that no command will wait.

Control hazard:

It arises due to the wrong decision on branch estimates in the pipeline. And as a result, the instruction that is carried to the pipeline will be cast off. The branch hazard is also known as the controlling hazard. It is also due to the instruction that affects the consecutive flow of control.

The subsequent instruction can decrease the controlling hazard

- Unqualified branches

- Conditional branches

- Indirect branches

- Process call

- Procedure returns

Hope you get the answer to the question “What is pipelining in computer architecture?”

See also Life is an open door?

The properties turns out

how to know what cbd oil to buy reddit

Has anyone shopped at Blackhat Vapor Shop? 🙂